Abstract

In the days of the vacuum tube we expected electronic devices to produce unwanted heat and then perform progressively poorly as the tubes aged and finally burnt-out. Transistors revolutionized the electronics industry in the 1950s with efficient, powerful, and reliable electronic systems. Transistors taught us to expect reliable energy efficient electronics devices. Modern electronic devices are leading people to unlearn some old lessons. Current advances in IC manufacturing technology threaten to derail our vision of a greener future with devices that recklessly squander millions of gigawatt hours of electrical energy yearly.

Up to three billion transistors fit into a single chip in 2011 and that transistor count will continue to double every two years with advances in IC manufacturing, according to Moore’s Law. Advances in IC manufacturing technology also bring higher clock speeds that let devices work faster and perform several tasks at the same time. While energy consumption does go up as the transistor count and the clock speed rises, this paper describes how advanced IC manufacturing technology transistor can bring more energy efficient devices.

Why are PC fan getting bigger and bigger? Why do laptops get hot? These are some troubling questions that give us a glimpse at emerging power and reliability issues. Advanced manufacturing technology can create energy efficient ICs, but there are becoming too many complex rules for IC designers to follow. Breaking, bending, and stretching the rules squanders power and accelerates time to failure.

This paper describes three generations of electronic energy conservation and the trend to squander more and more power that can cost the global economy trillions of dollars. The author envisions two response scenarios:

- Accepting Complacency. People are complacent about a global problem that they cannot see. People accept “good enough” battery life in mobile devices and that all electronic devices dissipate heat, breakdown and need to be replaced, while manufacturers respond to market demands.

- Reliable Green Chip Power. Individuals, nonprofit organizations and governments demand energy efficient reliable electronic devices. IC designers get the tools they need to follow all the manufacturing rules for reliability and energy efficiency.

Introduction

All electronic devices consume power according to two factors – design and use. It was easy to understand power consumption before transistors revolutionized the electronics industry. Tubes need to make heat in order to work properly and creating that heat consumes considerable power. Tubes devices consume power when on and consume no power when off. Transistors are the basic building blocks of the integrated circuits (ICs) in electronic devices. Unlike tubes, ICs work best when they are cool and only make heat to dissipate wasted electrical energy.

Understanding the power consumption of modern electronic devices is more complicated. Power-aware devices have ICs that dynamically manage power consumption according to how they are used. For example, smartphone power consumption changes according to the device mode and the applications running. Designing power- aware ICs takes extra time and increases the cost of manufacturing, since additional logic has to be added to save power by slowing down or powering down circuits not in use. Manufacturers use dynamic power management on the most power hungry components of mobile devices, where consumers are ready to pay a premium price for longer battery life. On stationary devices, customers accept larger fans to keep their systems cool systems instead of demanding greater power efficiency. As new IC manufacturing technology bring chips that consumer more and more electric power, the world needs another way to manage power and keep chips.

First generation power management is external to the device. “Turn the lights off when you’re not in the room,” is a simple first generation power management dictum. First generation power management relies on educating users to turn off their electronic devices. For example, turning off your computer at night would save power, but in practice it is more convenient to just leave it on.

Second generation power management is built into the logical and operational design of electronic devices. Engineers have a selection of methods to design devices that automatically save power depending on how they are used. But second generation power management does not address the fundamental power problem – all ICs waste electric power and that power consumption is increasing as manufacturing technology advances.

Third generation power management is about methodically designing ICs that always stay cool and efficient. Over the years, design engineers have developed many practical ad hoc methods to reduce the power that ICs waste. But refining IC designs for power efficiency takes time, so engineers only work to reduce power consumption until the results are good enough to bring to market. And as IC manufacturing technology advances it is becoming impractical to use ad hoc methods effectively. Third generation power management uses new tools like GBT’s Epsilon tool create a methodological approach for engineers to instantly design advanced ICs that stay cool and work reliably.

Background

You can think of a transistor as a little electric switch that consumers a tiny bit of energy every time it turns on or off. It is natural to think that power consumption is destined to be higher in an IC of similar design that has more transistors or operates at a higher speed. To meet this challenge, researchers have developed many different design techniques to reduce power. The complexity of today’s ICs, with over 100 million transistors, clocked at over 1 GHz, means efficient and automated power optimization is a must.

Low power consumption is one key features that led to the success of the CMOS technology now user in manufacturing most ICs. Designers could afford to concentrate on maximizing circuit performance and functionality without being too concerned about power efficiency. Another beneficial feature of CMOS technology is it’s nice scaling properties. Scaling allows designers to use old designs with in newer manufacturing technologies that have a smaller feature size. Think of scaling as reducing the size of an image on a page, leaving more open space for other things. SoC is the acronym we use to describe a complex System On a single Chip.

Power consumption started to become a concern with the appearance of the first portable electronic systems in the late 1980s, when consumers demanded longer battery life. High power consumption also creates heat dissipation problems requiring a fan or other heat removal systems.

Battery life and heat have made power consumption a major design parameter on par with performance and die size. In fact, power consumption has become the limiting factor in the continuing scaling of CMOS technology. To respond to this challenge, early research was invested in developing EDA tools for power optimization at the circuit and logic levels, where EDA tools are more mature the issues are easiest to handle. Today, there are several EDA tools that can be applied to power management at the system or architectural level.

Focus is returning to the circuit level in the latest power management EDA tools, because scaling does not work well as IC manufacturing technology advances to small nanometer geometries.

Electronic Power Consumption in Perspective

The terms power and energy are frequently confused. When a light bulb with a power rating of 100W is turned on for one hour, the energy used is 100 watt-hours (Wh) or 0.1 kilowatt-hours (kWh). Major power production or consumption is rated in megawatts or gigawatts.

The electrical energy wasted to heat by computer servers in one year is measured in petawatt hours (pWh). One petawatt hour is equal to 1,000 terawatt hours of energy (1,000 tWh). And one

terawatt hour of energy is approximately 114 megawatts of power sustained for a period of one full year.

The following four figures put some perspective of the cost of powering electronic devices.

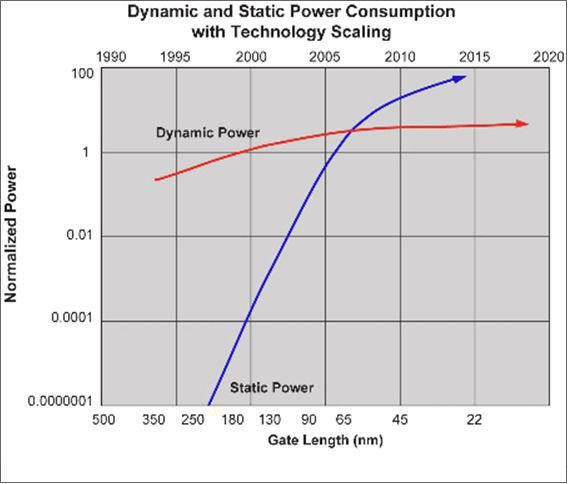

Image Source: Arnaud Tisserand, CNRS, IRISA laboratory

Image Source: US Energy Information Administration – 2008

Image Source: Lawrence Berkeley National Laboratory – 2008

Image Source: US Environmental Protection Agency – Aug. 2007

According to Dataquest, worldwide total power dissipation of processors in PCs was 160 megawatts in 1992, growing to 9000 megawatts by 2001. A typical server farm with 25000 square feet of space and 8000 servers is estimated to consume 2 megawatts of power. A computer owner in Britain demonstrated the extent of the thermal and heat density issues by placing a dish of aluminum foil above the chip inside his PC and frying an egg for breakfast in 11 minutes.

Power-Aware and Low Power Systems

Most power-aware and low-powers systems are mobile and battery powered. The resultant constraints on the energy budget require design-for-power as well as design-for performance at all layers of system design. Even when battery based constraints do not exist, energy must often be conserved in order to maintain continuous and reasonable working time.

Power-aware and low-power systems are different. Low-power designs aim to minimize the overall power consumption. Power-aware system aim to meet power and energy goals considering the system behavior based on current power availability. Power-aware design does not necessarily minimize the overall power consumption. In fact some power-aware design goals may increase power consumption.

Power Dissipation

When talking about IC power there is a constant race to achieve low power operation yet maintaining the design performance capabilities. The opportunities to reduce power improve as integrated circuits design is gearing towards system level. Rapid development of portable systems as laptops, PDAs, cellular phones, and other devices require low power consumption and high density ICs. As a result there is a rush of novel development in low power design techniques.

The total of power dissipation in CMOS technology is the sum of two factors:

- Static power dissipation occurs when a CMOS circuit is in an idle state. Although devices are not activated there is still some static power dissipation which is a result of leakage current through nominally off transistors. CMOS transistors have finite reverse leakage and sub-threshold currents. In an integrated circuit there are millions of transistors and the overall power dissipation due to nominally off transistors may be significant over time and is comparable to dynamic power dissipation. The values of leakage and sub-threshold currents are manufacturing process dependent.

- Dynamic power dissipation occurs when a MOS transistor switches to charge and discharge the output load capacitance at a particular node at operating frequency. Short-circuit power dissipation is a type of dynamic power dissipation that occurs during switching nMOS and pMOS transistors when they conduct at the same time and connect VDD to VSS. The current component that passes through both the nMOS and pMOS transistor during switching is called short circuit because it does not charge circuit capacitance.

When equipment power is turned on, ICs consume both dynamic power from transistor charging and static power from transistor leakage current. Lowering the overall chip power dissipation requires lowering both static and dynamic power. Power management design techniques involve a tradeoff among different parameters such as area, speed, and design time without impacting performance.

Image: ITRS

Static or standby power can be reduced by using the VTCMOS (Variable-Threshold-voltage CMOS) arrangement at the cost of extra bias control circuitry and substrate supply voltage, a strict requirement for laptops, PDAs and cellular phones that are required to be kept in standby mode for few hours. Power gating reduces leakage by shutting off power to individual circuits when they are not needed. Leakage power can be also be reduced by raising the transistor threshold voltage, but this simultaneously lowers transistor speed jeopardizing overall circuit functionality and performance. Power gating does not suffer from this drawback but requires additional circuitry for power management and control.

Voltage scaling reduces dynamic power dissipation, but could slow speed in some manufacturing technologies. It enforces designers to provide a safety margin to speed and power requirements. Dynamic power can be lowers by reduced clock implementing circuit parallelization and other switching reduction techniques.

The short circuit current is highly dependent on the input and output voltage values. Therefore the actual shape of the voltage signal waveforms at the input and output of the cell has to be considered in order to precisely calculate the short circuit energy dissipation. Typically, a pre-characterization process is executed for circuits to model their electrical parameters such as the

parasitic capacitances and nonlinear current sources in order to achieve an efficient power reduction and error-free operation.

As technology moves into deep nanometer arena leakage power is becoming a critical design issue. Leakage power is also strongly affected by on-chip process, temperature, and voltage variations. It has significant implications on IC performance, power management and reliability. In the past decade EDA tools evolved towards complete power management solution, taking into effect various electro-thermal couplings between supply voltage, threshold voltage, frequency, and junction temperature. New EDA tools also create a reliability and thermally aware design environment. For example, GBT’s Epsilon presents a reliability-aware design environment to probe physical phenomenon such as electromigration at early design stages. The tool also includes thermal consideration according to the chip’s region operating temperature.

Reliability-Aware Design Reduces Power

IC physical design is a key factor in overall power consumption. Creating a low-power physical design involves optimization and verification of the physical layout to meet goals including power, timing, performance, and area. While low-power design starts at the architectural level, the low-power design techniques continue through the physical layout; custom, semi-custom and synthesis. EDA physical design tools must interpret the power intent and analyze the layout to achieve a significant overall power reduction. While many tools target the more common low-power topics and techniques, designers should address the full spectrum of issues that can have a significant effect on power savings. Reliability verification (RV) is key part of the signal integrity (SI) domain that can reduce power.

Electromigration is the gradual displacement of metal atoms in a conductor. The primary causes are current density and temperature. As current flows through a wire, the movement of electrons interacts with metal ions in the conductor, and atoms are forced to move along with the flow of electrons. Poor electromigration design leads to thermal issues, impacting the overall power dissipation. Reliability-aware and temperature-aware designs are interrelated since temperature directly affects electromigration.

Temperature is proportional to power density. Methods to reduce thermal effects can either reduce power, increase area, or both. The common use of heat spreaders in modern high-performance microprocessors provides one example of increasing area to reduce power density and deal with thermal effects.

Design and system architecture define the application behavior and the chip thermal status to control execution rate, distribute the workload, and extract instruction-level parallelism. An efficient reliability analysis at the physical design level can identify and correct weak temperature related areas in order to avoid unnecessary power dissipation. The architecture can combine this information with dynamic information about electro migration and workload characteristics to precisely regulate temperature while minimizing performance loss. Addressing reliability at early stages of physical design phase can significantly contributes to the overall power savings. As a byproduct the entire design’s reliability and life time will meet higher standards and criteria.

Developing practical, affordable techniques to ensure reliability constraints has always been a challenge. It is especially critical with small nanometer IC manufacturing technologies, as problems require the introduction of new materials, new operating regions, and the reduction of reliability margins. The fact that efficient reliability design has a significant impact on IC power consumption makes use of a reliability EDA tools critically important.

Successful modern nanometer design requires reliability analysis built-in flow. Manual and routed interconnections must be reliability aware, taking physical effects such as SI into consideration on-the-fly. They must also be manufacturing-aware, with capabilities such as variable-spacing and variable-width routes to support copper, CMP, and sub-wavelength processes. Reliability and SI have become first-priority effects for successful tapeout. For the

past decade the EDA industry has provided extensive solutions for reliability phenomenon, yet significant improvement is needed in order to efficiently provide a unified solution, especially when an overall design’s power savings can be achieved.

In order to overcome advanced processes reliability, accomplishing power savings, new approaches have to be adopted. Instead of performing a global RV analysis on a large layout blocks, designer need tools to interactively check at an early stage. Designers can detect and correct reliability issues early in the design phase approaching signoff ready condition. Early detection of reliability issues is especially critical in custom and semi-custom layout design. The results of early detection include both significant power savings and a higher product yield.

Power Reduction and Efficient Electromigration Analysis

Effective power management techniques generally reduce electromigration, lower power dissipation and control voltage drop in ICs. DFM techniques that reduce variability also improve reliability. The main idea is to achieve a reliability-aware design without damaging the cost by causing overdesign characteristics.

Interactive extraction and analysis tools predict electromigration effects so engineers can make corrections in early design stages. Tools like GBT’s Epsilon work within the layout design platforms to produce virtually electromigration free physical design in digital, analog, and mixed-signal designs. Interactive reliability verification tools give designers the information they need to work faster and produce more reliable ICs that consumer much less power.

As the semiconductor manufacturing technology advances to the small nanometer electromigration and reliability with become critical issues as the CMOS technology is pushed to new low power and high performance limits.

A Simple Practical Example of Power Reduction

Here is a table showing seven sources of power consumption in a typical office computer:

| Power Consumption in Watts | |

| CPU | 80 |

| Memory | 36 |

| Disks | 12 |

| Peripherals | 50 |

| Motherboard | 25 |

| Fan | 10 |

| Leakage | 38 |

| Total | 251 |

- The CPU and memory consumer a total of 116 watts of electrical power.

- Here are five ways to reduce the CPU and memory power consumption:

- Interactive electromigration analysis and correction

- Better power-aware algorithms

- Better place and route technology

- Reduce frequency and activity factor

- Reduce power supply voltage

- Electromigration accounts for one sixth of the total power wasted in the PC chips.

- 19.33 (116/6) watts of energy are wasted by the CPU and memory in this typical PC example.

- The average PC in on eight hours a day according to the US Bureau of Labor Statistics http://www.bls.gov/news.release/atus.nr0.htm.

- “The number of installed PCs worldwide has surpassed 1 billion units in 2008, according to Gartner, Inc. Gartner analysts estimate the worldwide installed base of PCs is growing

just under 12 percent annually. At that pace, it will surpass 2 billion units by early 2014.” Gartner Web Site (http://www.gartner.com/it/page.jsp?id=703807)

- Server computers are on 24 hours a day

- According to Gartner (2007) Google has 1 million servers, which is about 2% of the whole world server number. In 2009 there were an estimated 44 million servers in the world. http://royal.pingdom.com/2009/08/24/google-may-own-more-than-2-of-all-servers-in-the-world/

- “On average, organizations get double the number of processors in each chip generation, approximately every two years. Each generation of microprocessor, with its doubling of processor counts through some combination of more cores and more threads per core, turns the same number of sockets into twice as many processors. In this way a 32-socket, high-end server with eight core chips in the sockets would deliver 256 processors in 2009. In two years, with 16 processors per socket appearing on the market, the machine swells to 512 processors in total. Four years from now, with 32 processors per socket shipping, that machine would host 1,024 processors.” Gartner press 2009 http://www.gartner.com/it/page.jsp?id=867112 http://www.pandia.com/sew/481-gartner.html

We estimate an average of 64 CPUs per server, taking into account older and newer servers.

- Average cost of one kilowatt hour (kWh) in the US was $0.10 in 2009 http://www.eia.doe.gov/cneaf/electricity/epm/table5_6_a.html

- One server wastes 10,848 kWh of power in a year of service due to electromigration.

19.33W x 64 (average number of CPUs in a server) x 24h x 365.25 days = 10,848 kWh

- Servers worldwide wasted 477 tWh of power due to electromigration in 2009.

10,848 kWh x 44 million servers worldwide = 477.312 tWh.

- $47.73B is the estimated cost of electrical power wasted by CPUs in servers worldwide due to electromigration in 2009.

4.77312 x 10e11 [ kWh] x 0.1 [ $/kW ] = $47.73B/Year

- $5.6 B is the estimated cost of electrical power wasted by personal PCs worldwide due to electromigration in 2008.

EM Power Consumption 1 PC = 19.33 W x 8 h [ Average PC Daily Usage ] x 365.25 days = 56 kWh/Year/PC

EM Power Consumption Worldwide = 56.482 kWh x 1 Billion PCs WW = 56.482 tWh

Cost of EM in PCs= 56.482 [kWh] x 10e9 x 0.1 [ $/kW ] = 5.6 $B/year

- $53.33B is the estimated cost of electrical power wasted by CPUs in servers; and CPUs and memory in PCs worldwide due to electromigration in 2009.

- The energy wasted on electromigration by electronic devices in 2011is measured in petawatt hours (thousands of terawatt hours).

Conclusions

Advanced IC manufacturing technology in small nanometers threatens to waste thousands and even millions of gigawatts of electrical power through electromigration. The global cost of electrical energy wasted on electromigration could reach into trillions of dollars a year. Energy wasted on electromigration pollutes the environments on a truly global scale.

IC reliability verification change to have a significant impact on power consumption. Consumers and businesses alike need to be educated to demand greater power efficiency from both mobile and stationary electronic device manufacturers. The world cannot afford to accepting complacency regarding electrical power needlessly wasted in ICs.

GBT is the world’s leading EDA vendor of interactive reliability and verification tools that reduce power consumption and bring more reliable product to market faster.

The third generation of power management starts with GBT’s Epsilon and results in reliable green chip power.

epsilon

APPROVED!

References

- K. Skadron et al., “Temperature-Aware Microarchitecture,” Proc. Int’l Symp. Computer Architecture (ISCA 2003), IEEE CS Press, 2003, pp. 2-13

- J. Srinivasan and S.V. Adve, “Predictive Dynamic Thermal Management for Multimedia Applications,” Proc. 17th Ann. ACM Int’l Conf. Supercomputing (ICS03), ACM Press, 2003.

- Balasubramonian, R., Dwarkadas, S., Albonesi, D., “Reducing the Complexity of the Register File in Dynamic Superscalar Processor”, in Proc. of the 34th Int’l. Symposium on Microarchitecture (MICRO–34), 2001.

- Borch, E., Tune, E., Manne, S., Emer, J., “Loose Loops Sink Chips”, in Proceedings of Int’l. Conference on High Performance Computer Architecture (HPCA–02), 2002.

- A. K. Coskun, T. Rosing, and K. Whisnant. “Temperature aware task scheduling in MPSoCs.” DATE, 2007.

- J. Donald and M. Martonosi. “Techniques for multicore thermal management: Classification and new exploration.” ISCA, 2006.

- M. Gomaa, M. D. Powell, and T. N. Vijaykumar. “Heat-and-Run: leveraging SMT and CMP to manage power density through the operating system.” ASPLOS, 2004.

- C. Isci, G. Contreras, and M. Martonosi. “Live, runtime phase monitoring and prediction on real systems with application to dynamic power management.” MICRO 39, 2006.

- R. Kumar, D. M. Tullsen, P. Ranganathan, N. P. Jouppi, and K. I. Farkas. ”Single-isa heterogeneous multi-core architectures for multithreaded workload performance.” ISCA, 2004.

- C. J. Lasance. “Thermally driven reliability issues in microelectronic systems: status-quo and challenges.” Microelectronics Reliability, 43:1969– 1974, 2003.

- A. S. Leon et al., “A Power-Efficient High-Throughput 32-Thread SPARC Processor,” IEEE JSSCC, vol.42, no.1, Jan. 2007

- S. Murali, A. Mutapcic, D. Atienza, R. Gupta, S. Boyd, L. Benini, and G. D. Micheli. “Temperature control of high-performance multicore platforms using convex optimization.” DATE, 2008.

- K. Skadron, M. Stan, W. Huang, S. Velusamy, K. Sankaranarayanan, and D. Tarjan. ”Temperature-aware microarchitecture.” ISCA, 2003

- C Kulkarni, F. Catthoor, H. De Man, “Code Transformations for Low Power Caching in Embedded Multimedia Processors”, International Parallel and Distributed Processing Symposium (IPPS/SPDP 98), Apr. 1998, pp.292-297.

- D Soudris, N. D. Zervas, A. Argyriou, M. Dasygenis, K. Tatas, C. Goutis, A. Twer, Real-Time Multimedia Applications”, IEEE International Workshop on Power and Timing Modeling, Optimization and Simulation, PATMOS’00, Sep. 2000, pp. 243- 254.

- O. S. Unsal, R. Ashok, I. Koren, C. M. Krishna, C. A. Moritz, Cool-Cache for Hot Multimedia”, 34th International Symposium on Microarchitecture MICRO34, Dec. 2001, pp. 274-283.

- O. S. Unsal, I. Koren, C. M. Krishna, C. A. Moritz, “The Minimax Cache: An Energy-Efficient Framework for Media Processors”, 8th International Symposium on High-Performance Computer Architecture, HPCA’02, Feb. 2002, pp. 131-140.

- Y. Li, W. Wolf, J. Henkel, “Task-level Memory Hierarchy Synthesis for Low Power in Real-Time Systems”, Proceedings of the 6th International Workshop on Hardware/Software Co-Design Codes/CASHE’98, Mar. 1998 (available athttp://www.ee.princeton.edu/˜ yanbing/ftp/codes98.ps).

- C. L. Liu, J. WW. Layland, “Scheduling Algorithms for Multiprogramming in a Hard Real Time Environment”, Journal of the ACM, Vol. 20, No. 1, pp. 46-61, 1973.

- F. Yao, A. Demers, S. Shenker, “A Scheduling Model for Reduced CPU Energy”, IEEE Annual Foundations of Computer Science, pp. 374-382, 1995.